### **General Description**

The MAX11008 controller biases RF LDMOS power devices found in cellular base stations and other wireless infrastructure equipment. Each controller includes a high-side current-sense amplifier with programmable gains of 2, 10, and 25 to monitor the LDMOS drain current over a range of 20mA to 5A. The MAX11008 supports up to two external diode-connected transistors to monitor the LDMOS temperatures while an internal temperature sensor measures the local die temperature. A 12-bit successive-approximation register (SAR) analogto-digital converter (ADC) converts the analog signals from the programmable-gain amplifiers (PGAs), external temperature sensors, internal temperature measurement, and two additional auxiliary inputs. The MAX11008 automatically adjusts the LDMOS bias voltages by applying temperature, AIN, and/or drain current samples to data stored in lookup tables (LUTs).

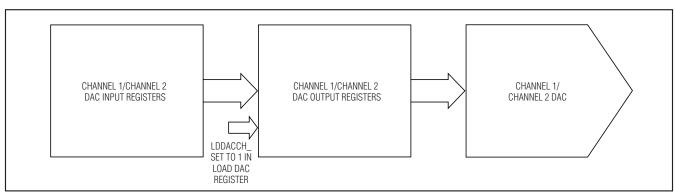

The MAX11008 includes two gate-drive channels, each consisting of a 12-bit DAC to generate the positive gate voltage for biasing the LDMOS devices. Each gatedrive output supplies up to ±2mA of gate current. The gate-drive amplifier is current-limited to ±25mA and features a fast clamp to AGND.

The MAX11008 contains 4Kb of on-chip, nonvolatile EEPROM organized as 256 bits x 16 bits to store LUTs and register information. The device operates from either a 4-wire 16MHz SPITM-/MICROWIRETM-compatible or an I<sup>2</sup>C-compatible serial interface.

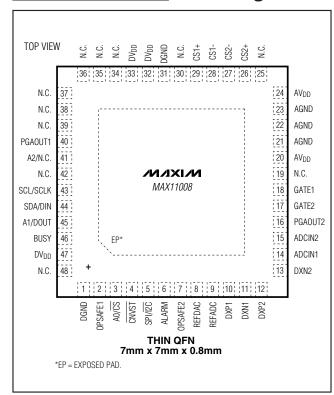

The MAX11008 operates from a +4.75V to +5.25V analog supply with a typical supply current of 2mA, and a +2.7V to +5.25V digital supply with a typical supply of 3mA. The device is packaged in a 48-pin, 7mm x 7mm, thin QFN package and operates over the extended (-40°C to +85°C) temperature range.

### **Applications**

Cellular Base Stations Microwave Radio Links Feed-Forward Power Amps **Transmitters** Industrial Process Control

#### **Features**

- ♦ On-Chip 4Kb EEPROM for Storing LDMOS Bias Characteristics

- ♦ Integrated High-Side Current-Sense PGA with Gain of 2, 10, or 25

- ♦ ±0.75% Accuracy for Sense Voltage Between +75mV and +1250mV

- ♦ Full-Scale Sense Voltage

- +100mV with a Gain of 25

- +250mV with a Gain of 10

- +1250mV with a Gain of 2

- **♦** Common-Mode Range, LDMOS Drain Voltage: +5V to +32V

- ♦ Adjustable Low-Noise 0 to AVDD Output Gate **Bias Voltage Range**

- **♦** Fast Clamp to AGND for LDMOS Protection

- **♦ 12-Bit DAC Control of Gate with Temperature**

- **♦ Internal Die Temperature Measurement**

- **♦ 2-Channel External Temperature Measurement** through Remote Diodes

- ♦ Internal 12-Bit ADC Measurement for Temperature, Current, and Voltage Monitoring

- ♦ User-Selectable Serial Interface 400kHz/1.7MHz/3.4MHz I<sup>2</sup>C-Compatible Interface 16MHz SPI-/MICROWIRE-Compatible Interface

### **Ordering Information**

| PART          | PIN-PACKAGE | TEMP<br>ERROR (°C) |

|---------------|-------------|--------------------|

| MAX11008BETM+ | 48 TQFN-EP* | ±3                 |

<sup>+</sup>Denotes a lead-free/RoHS-compliant package. \*EP = Exposed pad.

**Note:** The device is specified over the -40°C to +85°C operating temperature range.

SPI is a trademark of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp.

### **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD</sub> to AGND                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------|

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                     |

| 0.3V to the lower of (AV <sub>DD</sub> + 0.3V) and +6V<br>Digital Inputs/Outputs to DGND<br>(except SDA/DIN and SCL/SCLK) |

| SDA/DIN and SCL/SCLK to DGND                   | 0.3V to +6V   |

|------------------------------------------------|---------------|

| Continuous Input Current (all terminals)       | ±50mA         |

| Continuous Power Dissipation ( $T_A = +70$ °C) |               |

| 48-Pin, 7mm x 7mm, TQFN (derate 27.8m)         | W/°C above    |

| +70°C)                                         | 2222.2mW      |

| Operating Temperature Range                    | 40°C to +85°C |

| Junction Temperature                           | +150°C        |

| Storage Temperature Range                      |               |

| Lead Temperature (soldering, 10s)              | +300°C        |

|                                                |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CS\_+} = +32V, AV_{DD} = DV_{DD} = +5V \pm 5\%, external V_{REFADC} = +2.5V, external V_{REFDAC} = +2.5V, C_{REF} = 0.1\mu F, C_{GATE\_} = 0.1n F, V_{SENSE} = V_{CS\_+} - V_{CS\_-}, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                              | SYMBOL                                   | CONDITIONS                                                    | MIN | TYP  | MAX   | UNITS |  |  |  |

|--------------------------------------------------------|------------------------------------------|---------------------------------------------------------------|-----|------|-------|-------|--|--|--|

| HIGH-SIDE CURRENT-SENSE PGA                            |                                          |                                                               |     |      |       |       |  |  |  |

| Common-Mode Input Voltage<br>Range                     | V <sub>CS1+</sub> ,<br>V <sub>CS2+</sub> |                                                               | 5   |      | 32    | V     |  |  |  |

| Common-Mode Rejection Ratio                            | CMRR                                     | 5V < V <sub>CS_+</sub> < 32V                                  |     | 110  |       | dB    |  |  |  |

| CS_+ Input Bias Current                                | ICS_+                                    | VSENSE < 100mV over the common-mode range                     |     | 135  | 195   | μΑ    |  |  |  |

| CS Input Bias Current                                  | I <sub>CS</sub>                          | VSENSE < 100mV over the common-mode range                     |     |      | ±1    | μΑ    |  |  |  |

| Full-Scale Sense Voltage Range                         |                                          | Gain = 25                                                     | 0   |      | 100   |       |  |  |  |

|                                                        | VSENSE                                   | Gain = 10                                                     | 0   |      | 250   | mV    |  |  |  |

|                                                        |                                          | Gain = 2                                                      | 0   |      | 1250  |       |  |  |  |

| Minimum Canada Valhama Banan                           |                                          | Gain = 25                                                     | 75  |      | 100   |       |  |  |  |

| Minimum Sense Voltage Range for ±0.75% VSENSE Accuracy |                                          | Gain = 10                                                     | 75  |      | 250   | mV    |  |  |  |

| 101 10.73% VSENSE / Recuracy                           |                                          | Gain = 2                                                      | 75  |      | 1250  |       |  |  |  |

|                                                        |                                          | Gain = 25                                                     | 20  |      | 100   |       |  |  |  |

| Minimum Sense Voltage Range for ±2.5% VSENSE Accuracy  |                                          | Gain = 10                                                     | 20  |      | 250   | mV    |  |  |  |

| 101 12.3 % VSENSE Accuracy                             |                                          | Gain = 2                                                      | 20  |      | 1250  |       |  |  |  |

| Total PGAOUT Voltage Error                             |                                          | V <sub>SENSE</sub> = 75mV                                     |     | ±0.1 | ±0.75 | %     |  |  |  |

| PGAOUT Capacitive Load                                 | CPGAOUT                                  |                                                               |     |      | 50    | pF    |  |  |  |

| PGAOUT Settling Time                                   | tHSCS                                    | (Note 1)                                                      |     | < 25 |       | μs    |  |  |  |

| Saturation Recovery Time                               |                                          | Settles to within ±0.5% accuracy from VSENSE = 3 x full scale |     | < 45 |       | μs    |  |  |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CS\_+} = +32V, AV_{DD} = DV_{DD} = +5V \pm 5\%, external V_{REFADC} = +2.5V, external V_{REFDAC} = +2.5V, C_{REF} = 0.1\mu F, C_{GATE\_} = 0.1nF, V_{SENSE} = V_{CS\_+} - V_{CS\_-}, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                | SYMBOL             | CONDITIONS                                                                              | MIN    | TYP    | MAX                        | UNITS             |

|------------------------------------------|--------------------|-----------------------------------------------------------------------------------------|--------|--------|----------------------------|-------------------|

| LDMOS GATE DRIVER (Gain = 2)             | ·<br>·             |                                                                                         |        |        |                            |                   |

| Output Cata Priva Valtaga Panga          | \\o.+==            | IGATE_ = ±0.1mA                                                                         | 0.1    |        | AV <sub>DD</sub> - 0.1     | V                 |

| Output Gate-Drive Voltage Range          | VGATE_             | IGATE_ = ±2mA                                                                           | 0.75   |        | AV <sub>DD</sub> -<br>0.75 | V                 |

| Output Impedance                         | RGATE_             | Measured at DC                                                                          |        | 0.1    |                            | Ω                 |

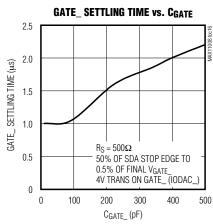

| GATE_ Settling Time                      | tGATE_             | $R_S = 500\Omega$ , $C_{GATE} = 15\mu F$ , $V_{GATE} = 0.5V$ to 4.5V (Note 1)           |        | 45     |                            | ms                |

| Output Capacitive Load                   | CGATE_             | Rseries = $0\Omega$                                                                     | 0      |        | 0.5                        | nF                |

|                                          | G/ 11              | RSERIES = $500\Omega$                                                                   | 0      | 15,000 |                            |                   |

| GATE_ Noise                              | I                  | 1kHz to 1MHz                                                                            |        | 1000   |                            | μV <sub>P-P</sub> |

| Maximum Power-On Transient               |                    |                                                                                         |        | ±100   |                            | mV                |

| Output Short-Circuit Current Limit       | Isc                | 1s, sinking or sourcing                                                                 |        | ±25    |                            | mA                |

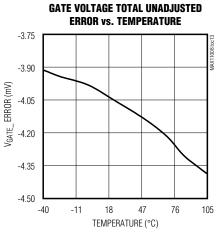

| Total Unadjusted Error                   | TUE                | Worst case at CODE = 4063, use external reference (Note 2)                              |        | ±7     | ±25                        | mV                |

| Total Unadjusted Error without<br>Offset | TUENO_OFFSET       | CalCODE = 2457, MaxCODE = 2867, use external reference, T <sub>A</sub> = +25°C (Note 2) |        |        | 8±                         | mV                |

| Drift                                    |                    | Gain = 2, MaxCODE = 2867 (Note 2)                                                       |        | ±15    |                            | μV/°C             |

| Clamp to Zero Delay                      |                    | CGATE_ = 0.5nF (Note 3)                                                                 |        | 1      |                            | μs                |

| Output-Safe Switch On-<br>Resistance     | Ropsw              | V <sub>GATE</sub> _ clamped to AGND (Note 4)                                            |        | 300    |                            | Ω                 |

| MONITOR ADC (DC characteristi            | cs)                |                                                                                         |        |        |                            |                   |

| Resolution                               | Nadc               |                                                                                         | 12     |        |                            | Bits              |

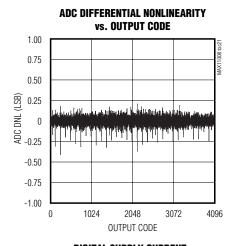

| Differential Nonlinearity                | DNL <sub>ADC</sub> | (Note 5)                                                                                | -2     |        | +2                         | LSB               |

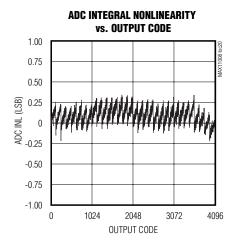

| Integral Nonlinearity                    | INL <sub>ADC</sub> |                                                                                         |        |        | ±2                         | LSB               |

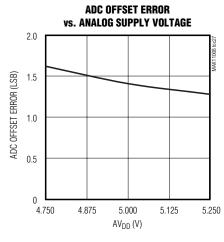

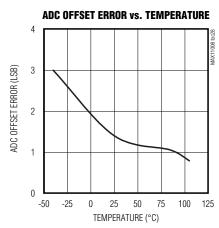

| Offset Error                             |                    |                                                                                         |        | ±2     | ±4                         | LSB               |

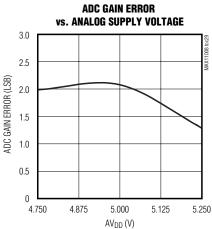

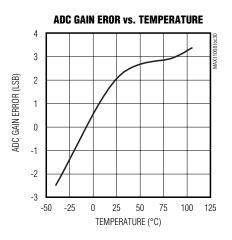

| Gain Error                               |                    | (Note 6)                                                                                |        | ±2     | ±4                         | LSB               |

| Gain Temperature Coefficient             |                    |                                                                                         |        | ±0.4   |                            | ppm/°C            |

| Offset Temperature Coefficient           |                    |                                                                                         |        | ±0.4   |                            | ppm/°C            |

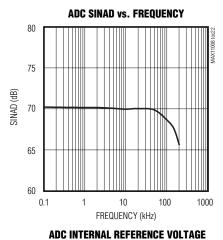

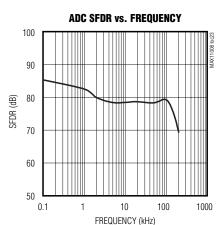

| MONITOR ADC DYNAMIC CHARA                | ACTERISTICS (1     | kHz sine-wave input, 2.5V <sub>P-P</sub> , up to 94.4                                   | lksps) |        |                            |                   |

| Signal-to-Noise Plus Distortion          | SINAD              |                                                                                         |        | 70     |                            | dB                |

| Total Harmonic Distortion                | THD                | Up to 5th harmonic                                                                      |        | -82    |                            | dBc               |

| Spurious-Free Dynamic Range              | SFDR               |                                                                                         |        | 86     |                            | dBc               |

| Intermodulation Distortion               | IMD                | $f_{\text{IN1}} = 0.99 \text{kHz}, f_{\text{IN2}} = 1.02 \text{kHz}$                    |        | 76     |                            | dBc               |

| Full-Power Bandwidth                     |                    | -3dB                                                                                    |        | 1      |                            | MHz               |

| Full-Linear Bandwidth                    |                    | SINAD > 68dB                                                                            |        | 100    |                            | kHz               |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CS\_+} = +32V, \ AV_{DD} = DV_{DD} = +5V \ \pm 5\%, \ external \ V_{REFADC} = +2.5V, \ external \ V_{REFDAC} = +2.5V, \ C_{REF} = 0.1\mu\text{F}, \ C_{GATE\_} = 0.1n\text{F}, \ V_{SENSE} = V_{CS\_+} - V_{CS\_-}, \ T_A = -40^{\circ}\text{C} \ to \ +85^{\circ}\text{C}, \ unless \ otherwise \ noted.}$

| PARAMETER                             | SYMBOL                                         | CONDITIONS                                                               | MIN  | TYP   | MAX              | UNITS  |

|---------------------------------------|------------------------------------------------|--------------------------------------------------------------------------|------|-------|------------------|--------|

| MONITOR ADC CONVERSION RA             | ATE                                            |                                                                          |      |       |                  | -      |

| Power-Up Time (External<br>Reference) | tpuext                                         |                                                                          |      | 1.1   |                  | μs     |

| Power-Up Time (Internal Reference)    | tpuint                                         |                                                                          |      | 70    |                  | μs     |

| Acquisition Time                      | tACQ                                           |                                                                          |      | 0.5   |                  | μs     |

| Conversion Time                       | tconv                                          | Internally clocked, T <sub>A</sub> = +25°C                               |      |       | 10               | μs     |

| Aperture Delay                        | t <sub>AD</sub>                                |                                                                          |      | 20    |                  | ns     |

| MONITOR ADC ANALOG INPUT (            | ADCIN1, AD                                     | CIN2)                                                                    |      |       |                  |        |

| Input Voltage Range                   | Vadcin                                         | Relative to AGND (Note 7)                                                | 0    |       | VREFADC          | V      |

| Input Leakage Current                 |                                                | V <sub>IN</sub> = 0 and V <sub>IN</sub> = V <sub>A</sub> V <sub>DD</sub> |      | ±0.01 |                  | μΑ     |

| Input Capacitance                     | Cadcin                                         |                                                                          |      | 34    |                  | рF     |

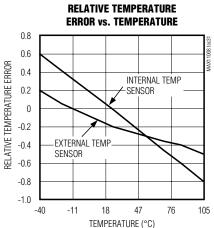

| TEMPERATURE MEASUREMENT               | s                                              |                                                                          |      |       |                  |        |

| Internal Sensor Measurement           |                                                | T <sub>A</sub> = +25°C                                                   |      | ±0.25 |                  | 00     |

| Error                                 |                                                | T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub> (Note 8)           |      | ±1.5  | ±3               | °C     |

| External Sensor Measurement           |                                                | T <sub>A</sub> = +25°C                                                   |      | ±1    |                  | 00     |

| Error (Note 9)                        |                                                | $T_A = T_{MIN}$ to $T_{MAX}$                                             |      | ±3    |                  | °C     |

| Relative Temperature Accuracy         |                                                | $T_A = T_{MIN}$ to $T_{MAX}$ (Note 9)                                    |      | ±0.4  |                  | °C     |

| Temperature Resolution                |                                                |                                                                          |      | 1/8   |                  | °C/LSB |

| External Diode Drive Current (Low)    |                                                |                                                                          | 3.25 | 4     |                  | μΑ     |

| External Diode Drive Current (High)   |                                                |                                                                          |      | 68    | 75               | μΑ     |

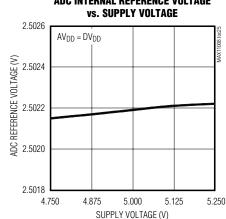

| INTERNAL REFERENCE                    |                                                |                                                                          |      |       |                  |        |

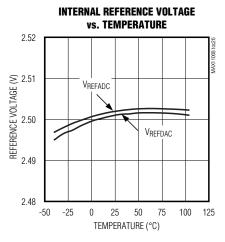

| REFADC/REFDAC Output<br>Voltage       | VREFADC,<br>VREFDAC                            | T <sub>A</sub> = +25°C                                                   | 2.49 | 2.50  | 2.51             | V      |

| REFADC/REFDAC Temperature Coefficient | TC <sub>REFDAC</sub> ,<br>TC <sub>REFDAC</sub> |                                                                          |      | ±15   |                  | ppm/°C |

| REFADC/REFDAC Output Impedance        |                                                |                                                                          |      | 6.5   |                  | kΩ     |

| Capacitive Bypass at REFADC/REFDAC    |                                                |                                                                          | 270  |       |                  | рF     |

| Power-Supply Rejection Ratio          | PSRR                                           | $AV_{DD} = 5V \pm 5\%$                                                   |      | 64    |                  | dB     |

| EXTERNAL REFERENCE                    | •                                              |                                                                          | •    |       |                  |        |

| REFADC Input Voltage Range            | VREFADC                                        |                                                                          | 1.0  |       | AV <sub>DD</sub> | V      |

| DEEADO Israel O                       |                                                | VREFADC = 2.5V, fSAMPLE = 100ksps                                        |      | 60    | 80               |        |

| REFADC Input Current                  | IREFADC                                        | Acquisition/between conversions                                          |      | ±0.01 |                  | μΑ     |

| REFDAC Input Voltage Range            | VREFDAC                                        |                                                                          | 0.7  |       | 2.5              | V      |

| REFDAC Input Current                  |                                                | Static current when the DAC is not calibrated                            |      | 0.1   |                  | μΑ     |

. \_\_\_\_\_ NIXIM

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CS\_+} = +32V, AV_{DD} = DV_{DD} = +5V \pm 5\%, external V_{REFADC} = +2.5V, external V_{REFDAC} = +2.5V, C_{REF} = 0.1\mu F, C_{GATE\_} = 0.1nF, V_{SENSE} = V_{CS\_+} - V_{CS\_-}, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                    | SYMBOL             | CONDITIONS                                            | MIN                        | TYP  | MAX                       | UNITS |

|------------------------------|--------------------|-------------------------------------------------------|----------------------------|------|---------------------------|-------|

| GATE-DRIVER DAC DC ACCURA    | ACY                |                                                       |                            |      |                           |       |

| Resolution                   | NDAC               |                                                       | 12                         |      |                           | Bits  |

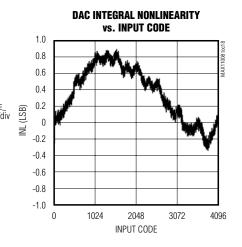

| Integral Nonlinearity        | INL <sub>DAC</sub> | Measured at GATE_                                     |                            | ±2   | ±4                        | LSB   |

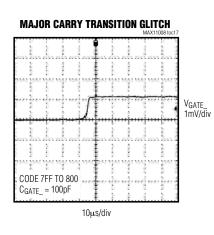

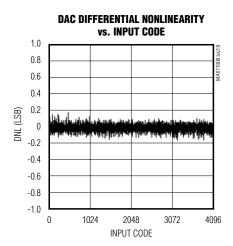

| Differential Nonlinearity    | DNL <sub>DAC</sub> | Guaranteed monotonic (Note 10)                        |                            |      | ±1                        | LSB   |

| DIGITAL INPUTS (SCL/SCLK, SI | DA/DIN, A0/C       | S, A1/DOUT, A2/N.C., CNVST, OPSAFE1, OP               | SAFE2)                     |      |                           |       |

|                              | VIH                | SDA/DIN and SCL/SCLK only                             | 0.7 x<br>DV <sub>DD</sub>  |      |                           | V     |

| Input High Voltage           | VIH                | A0/CS, A1/DOUT, A2/N.C., CNVST, OPSAFE1, OPSAFE2 only | 2.3                        |      |                           | V     |

| Input Low Voltage            | VIL                | SDA/DIN and SCL/SCLK only                             |                            |      | 0.3 x<br>DV <sub>DD</sub> | V     |

|                              | VIL                | A0/CS, A1/DOUT, A2/N.C., CNVST, OPSAFE1, OPSAFE2 only |                            |      | 0.7                       | V     |

| Input Hysteresis             | V <sub>H</sub> YS  | SDA/DIN and SCL/SCLK only                             | 0.08 x<br>DV <sub>DD</sub> |      |                           | V     |

| Input Leakage Current        |                    | Digital inputs at 0 or V <sub>DVDD</sub>              |                            | ±0.1 | ±1                        | μΑ    |

| Input Capacitance            | CIN                |                                                       |                            | 5    |                           | рF    |

| DIGITAL OUTPUTS (SDA/DIN, A  | LARM, BUSY         | , DOUT)                                               |                            |      |                           |       |

| Output High Voltage          | VoH                | ALARM and BUSY only, ISOURCE = 0.2mA                  | DV <sub>DD</sub><br>- 0.4V |      |                           | V     |

| Output Low Voltage           | V <sub>OL</sub>    | SDA/DIN and A1/DOUT, ISINK = 3mA, (Note 11)           |                            |      | 0.4                       | V     |

|                              |                    | ALARM and BUSY only, ISINK = 0.3mA                    |                            |      | 0.3                       |       |

| Three-State Leakage          | IIL                | Digital inputs at 0 or DV <sub>DD</sub>               |                            | ±0.1 | ±1                        | μΑ    |

| Three-State Capacitance      |                    |                                                       |                            | 5    |                           | рF    |

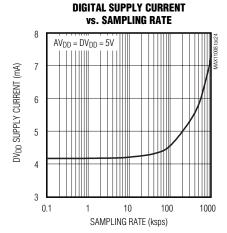

| POWER SUPPLIES (Note 12)     |                    |                                                       |                            |      |                           |       |

| Analog Supply Voltage Range  | AV <sub>DD</sub>   |                                                       | 4.75                       |      | 5.25                      | V     |

| Digital Supply Voltage Range | DV <sub>DD</sub>   |                                                       | 2.7                        |      | AV <sub>DD</sub><br>+ 0.3 | V     |

| Analog Supply Current        | 1                  | $AV_{DD} = 5V$                                        |                            | 2    | 4                         | mA    |

| Analog Supply Current        | lavdd              | Shutdown (Note 13)                                    |                            | 0.4  | 2                         | μΑ    |

| Digital Supply Current       | In the             | $DV_{DD} = 5V$                                        |                            | 3    | 6                         | mA    |

| Digital Supply Current       | IDVDD              | Shutdown                                              |                            | 2    | 32                        | μΑ    |

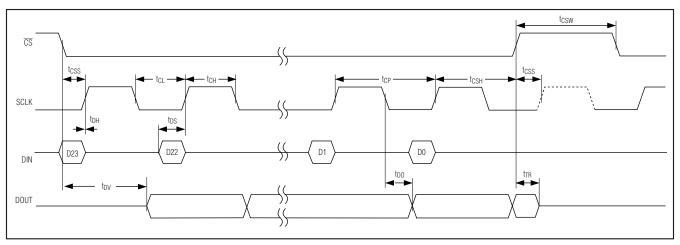

### **SPI TIMING CHARACTERISTICS (Notes 14, 15, Figure 1)**

$(DV_{DD} = +2.7V \text{ to } +5.25V, \text{AV}_{DD} = +4.75V \text{ to } +5.25V, \text{V}_{DGND} = \text{V}_{AGND} = 0$ , external  $V_{REFADC} = +2.5V$ , external  $V_{REFDAC} = +2.5V$ , external  $V_{REFDAC}$

| PARAMETER                    | SYMBOL          | CONDITIONS                      | MIN  | TYP | MAX | UNITS |

|------------------------------|-----------------|---------------------------------|------|-----|-----|-------|

| SCLK Clock Period            | tcp             |                                 | 62.5 |     |     | ns    |

| SCLK High Time               | tсн             |                                 | 25   |     |     | ns    |

| SCLK Low Time                | tcL             |                                 | 25   |     |     | ns    |

| DIN to SCLK Rise Setup Time  | t <sub>DS</sub> |                                 | 15   |     |     | ns    |

| DIN to SCLK Rise Hold Time   | tDH             |                                 | 0    |     |     | ns    |

| SCLK Fall to DOUT Transition | t <sub>DO</sub> | $C_L = 30pF$                    |      |     | 20  | ns    |

| CS Fall to DOUT Enable       | t <sub>DV</sub> | $C_L = 30pF$                    |      |     | 50  | ns    |

| CS Rise to DOUT Disable      | t <sub>TR</sub> | C <sub>L</sub> = 30pF (Note 16) |      |     | 50  | ns    |

| CS Rise or Fall to SCLK Rise | tcss            |                                 | 12.5 |     |     | ns    |

| CS Pulse-Width High          | tcsw            |                                 | 50   |     |     | ns    |

| Last SCLK Rise to CS Rise    | tcsh            |                                 | 0    |     |     | ns    |

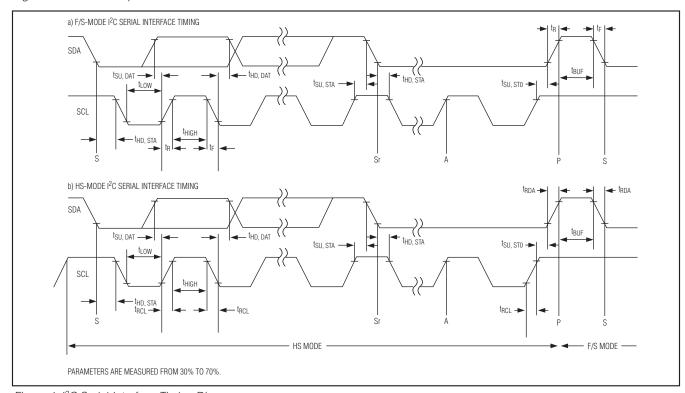

### I<sup>2</sup>C SLOW-/FAST-MODE TIMING CHARACTERISTICS (Notes 14, 15, Figure 4)

$(DV_{DD} = +2.7V \ to \ +5.25V, \ AV_{DD} = +4.75V \ to \ +5.25V, \ V_{DGND} = V_{AGND} = 0, \ external \ V_{REFADC} = +2.5V, \ external \ V_{REFDAC} = +2.5V, \ ex$

| PARAMETER                                               | SYMBOL         | CONDITIONS                                            | MIN                          | TYP | MAX | UNITS |

|---------------------------------------------------------|----------------|-------------------------------------------------------|------------------------------|-----|-----|-------|

| SCL Clock Frequency                                     | fscl           |                                                       | 0                            |     | 400 | kHz   |

| Bus Free Time Between a STOP and START Condition        | tBUF           |                                                       | 1.3                          |     |     | μs    |

| Hold Time (Repeated) for START Condition                | thd:STA        | After this period, the first clock pulse is generated | 0.6                          |     |     | μs    |

| Setup Time for a Repeated<br>START Condition            | tsu:sta        |                                                       | 0.6                          |     |     | μs    |

| SCL Pulse-Width Low                                     | tLOW           |                                                       | 1.3                          |     |     | μs    |

| SCL Pulse-Width High                                    | tHIGH          |                                                       | 0.6                          |     |     | μs    |

| Data Setup Time                                         | tsu:dat        |                                                       | 100                          |     |     | ns    |

| Data Hold Time                                          | thd:dat        | (Note 17)                                             | 0.004                        |     | 0.9 | μs    |

| SDA, SCL Rise Time                                      | t <sub>R</sub> | Receiving (Note 18)                                   | 0                            |     | 300 | ns    |

| SDA, SCL Fall Time                                      | t <sub>F</sub> | Receiving (Note 18)                                   | 0                            |     | 300 | ns    |

| SDA Fall Time                                           | tF             | Transmitting (Notes 18, 19)                           | 20 + 0.1<br>x C <sub>B</sub> |     | 250 | ns    |

| Setup Time for STOP Condition                           | tsu:sto        |                                                       | 0.6                          |     |     | μs    |

| Capacitive Load for Each Bus<br>Line                    | СВ             | (Note 20)                                             |                              |     | 400 | pF    |

| Pulse Width of Spikes<br>Suppressed by the Input Filter | tsp            | (Note 21)                                             |                              |     | 50  | ns    |

### I<sup>2</sup>C HIGH-SPEED-MODE TIMING CHARACTERISTICS (Notes 14, 15, Figure 4)

$(DV_{DD} = +2.7V \text{ to } +5.25V, \text{ AV}_{DD} = +4.75V \text{ to } +5.25V, V_{DGND} = V_{AGND} = 0$ , external  $V_{REFADC} = +2.5V$ , external  $V_{REFDAC} = +2.5V$ ,  $V_{REF} = 0.1\mu F$ ,  $V_{REF} = -40^{\circ} C$  to  $+85^{\circ} C$ , unless otherwise noted.)

| DADAMETED                                            | OVMDO             | CONDITIONS                                                    | C <sub>B</sub> = 10 | C <sub>B</sub> = 100pF max |     | 400pF | LINITO |

|------------------------------------------------------|-------------------|---------------------------------------------------------------|---------------------|----------------------------|-----|-------|--------|

| PARAMETER                                            | SYMBOL            | CONDITIONS                                                    | MIN                 | MAX                        | MIN | MAX   | UNITS  |

| Serial Clock Frequency                               | f <sub>SCL</sub>  |                                                               | 0                   | 3.4                        | 0   | 1.7   | MHz    |

| Setup Time (Repeated) START Condition                | tsu:sta           |                                                               | 160                 |                            | 160 |       | ns     |

| Hold Time (Repeated) START Condition                 | tHD:STA           |                                                               | 160                 |                            | 160 |       | ns     |

| SCL Pulse-Width Low                                  | tLOW              |                                                               | 160                 |                            | 320 |       | ns     |

| SCL Pulse-Width High                                 | <sup>t</sup> HIGH |                                                               | 80                  |                            | 120 |       | ns     |

| Data Setup Time                                      | tsu:dat           |                                                               | 10                  |                            | 10  |       | ns     |

| Data Hold Time                                       | thd:dat           | (Note 17)                                                     | 4                   | 70                         | 4   | 150   | ns     |

| SCL Rise Time                                        | tRCL              |                                                               | 10                  | 40                         | 20  | 80    | ns     |

| SCL Rise Time                                        | <sup>t</sup> RCL1 | After a repeated START condition and after an acknowledge bit | 10                  | 80                         | 20  | 160   | ns     |

| SCL Fall Time                                        | tFCL              |                                                               | 10                  | 40                         | 20  | 80    | ns     |

| SDA Rise Time                                        | trda              |                                                               | 10                  | 80                         | 20  | 160   | ns     |

| SDA Fall Time                                        | t <sub>FDA</sub>  |                                                               | 10                  | 80                         | 20  | 160   | ns     |

| Setup Time for STOP Condition                        | tsu:sto           |                                                               | 160                 |                            | 160 |       | ns     |

| Capacitive Load for Each Bus Line                    | CB                | (Note 20)                                                     |                     | 100                        |     | 400   | ns     |

| Pulse Width of Spikes Suppressed by the Input Filter | tsp               | (Note 21)                                                     | 0                   | 10                         | 0   | 10    | ns     |

### **MISCELLANEOUS TIMING CHARACTERISTICS (Note 15)**

(DVDD = +2.7V to +5.25V, AVDD = +4.75V to +5.25V, VDGND = VAGND = 0, external VREFADC = +2.5V, external VREFDAC = +2.5V, CREF = 0.1 $\mu$ F, TA = -40°C to +85°C, unless otherwise noted.)

| PARAMETER                                                                                        | SYMBOL            | CONDITIONS | MIN | TYP | MAX | UNITS |

|--------------------------------------------------------------------------------------------------|-------------------|------------|-----|-----|-----|-------|

| Minimum Time to Wait After a Write<br>Command Before Reading Back<br>Data from the Same Location | <sup>t</sup> RDBK | (Note 22)  |     | 1   |     | μs    |

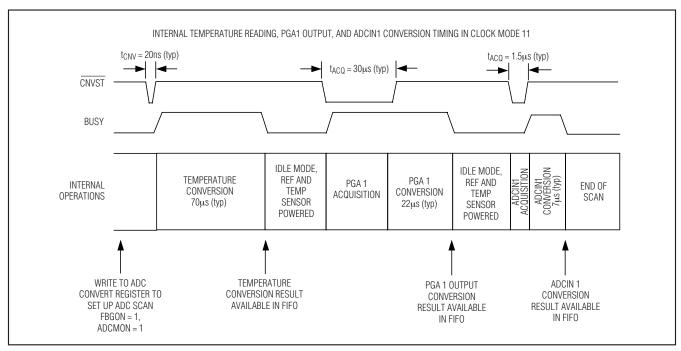

| CNVST Active-Low Pulse Width in ADC Clock Mode 01                                                | tCNV01            |            | 20  |     |     | ns    |

| CNVST Active-Low Pulse Width in ADC Clock Mode 11 to Initiate a Temperature Conversion           | tCNV11            |            | 20  |     |     | ns    |

| CNVST Active-Low Pulse Width in ADC Clock Mode 11 for ADCIN1/2 Acquisition                       | tACQ11A           |            | 1.5 |     |     | μs    |

| ADC Power-Up Time (External Reference)                                                           | tapuext           |            |     | 1.1 |     | μs    |

| ADC Power-Up Time (Internal Reference)                                                           | tapuint           |            |     | 70  |     | μs    |

### **MISCELLANEOUS TIMING CHARACTERISTICS (Note 15) (continued)**

$(DV_{DD} = +2.7V \text{ to } +5.25V, \text{AV}_{DD} = +4.75V \text{ to } +5.25V, \text{V}_{DGND} = \text{V}_{AGND} = 0$ , external  $V_{REFADC} = +2.5V$ , external  $V_{REFDAC} = +2.5V$ , external  $V_{REFDAC}$

| PARAMETER                                                       | SYMBOL  | CONDITIONS                                 | MIN | TYP | MAX | UNITS |

|-----------------------------------------------------------------|---------|--------------------------------------------|-----|-----|-----|-------|

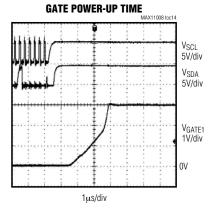

| DAC Power-Up Time (External Reference)                          | tDPUEXT |                                            |     | 2   |     | μs    |

| DAC Power-Up Time (Internal Reference)                          | tdpuint |                                            |     | 70  |     | μs    |

| Acquisition Time (Internally Timed in ADC Clock Modes 00 or 01) | tACQ    |                                            |     |     | 0.6 | μs    |

| Conversion Time (Internally Clocked)                            | tCONV   | Internally clocked, T <sub>A</sub> = +25°C |     |     | 10  | μs    |

| Delay to Start of Conversion Time                               | tconvw  | (Note 23)                                  |     | 1.3 |     | μs    |

| Temperature Conversion Time (Internally Clocked)                | tCONVT  |                                            |     | 70  |     | μs    |

- **Note 1:** Output settles to within  $\pm 0.5\%$  of final value.

- **Note 2:** Total unadjusted errors are for the entire gate-drive channel including the 12-bit DAC, and the gate driver is measured at the GATE1 and GATE2 outputs.

- **Note 3:** V<sub>GATE</sub> = V<sub>DD</sub> 0.1. Measured from when OPSAFE1 or OPSAFE2 is set high.

- Note 4: During power-on-reset, the output safe switch is closed. The output safe switch is opened under user software control.

- Note 5: Guaranteed to be 11 bits linearly accurate.

- Note 6: Offset nulled.

- Note 7: The absolute range for analog inputs is from 0 to VAVDD.

- Note 8: Internal temperature-sensor performance is guaranteed by design.

- **Note 9:** The MAX11008 and the external sensor are at the same ambient temperature. External sensor measurement error is tested with a diode-connected 2N3904.

- **Note 10:** Guaranteed monotonicity. Accuracy is degraded at lower V<sub>REFDAC</sub>.

- Note 11: SDA/DIN is an open-drain output only when in I<sup>2</sup>C mode. A1/DOUT is an open-drain output only when in SPI mode.

- **Note 12:** Supply-current limits are valid only when digital inputs are set to DGND or supply voltage. Timing specifications are only guaranteed when inputs are driven rail-to-rail.

- Note 13: Shutdown supply currents are typically 0.4µA for AVDD; maximum specification is limited by automated test equipment.

- Note 14: All times are referred to the 50% point between  $V_{IH}$  and  $V_{IL}$  levels.

- Note 15: Guaranteed by design. Not production tested.

- Note 16: DOUT will go into three-state mode after the  $\overline{CS}$  rising edge. Keep  $\overline{CS}$  low long enough for the DOUT value to be sampled before it goes to three-state.

- Note 17: A master device must provide a hold time of at least 300ns for the SDA signal (referred to V<sub>IL</sub> of the SCL signal) to bridge the undefined region of SCL's falling edge.

- **Note 18:**  $t_R$  and  $t_F$  measured between 0.3 x DV<sub>DD</sub> and 0.7 x DV<sub>DD</sub>.

- Note 19: C<sub>B</sub> = total capacitance of one bus line in pF. For bus loads between 100pF and 400pF, the timing parameters should be linearly interpolated.

- Note 20: An appropriate bus pullup resistance must be selected depending on board capacitance.

- Note 21: Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

- Note 22: When a command is written to the serial interface, the command is passed by the internal oscillator clock and executed. There is a small synchronization delay before the new value is written to the appropriate register. If the serial interface attempts to read the new value back before transfer the new data is not corrupted; however, the result of the read command may not reflect the new value.

- Note 23: This is the minimum time from the end of a command before  $\overline{\text{CNVST}}$  should be asserted. The time allows for the data from the preceding write to arrive and set up the chip in preparation for the  $\overline{\text{CNVST}}$ . The time need only be observed when the write affects the ADC controls. Failure to observe this time may lead to incorrect conversions (for example, conversion of the wrong ADC channel).

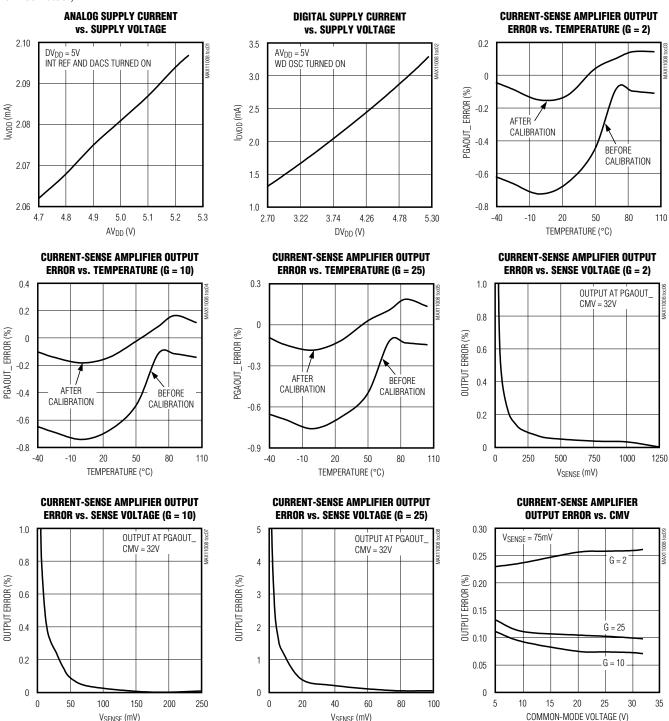

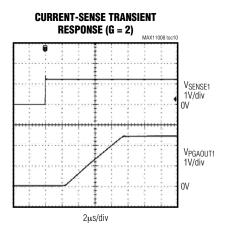

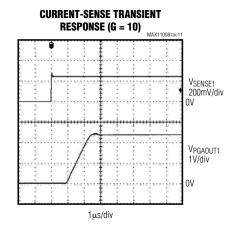

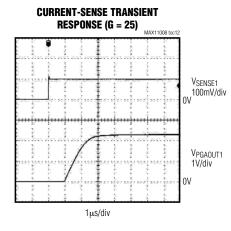

### **Typical Operating Characteristics**

(AVDD = DVDD = 5V, external V<sub>REFADC</sub> = 2.5V, external V<sub>REFDAC</sub> = 2.5V, V<sub>CS</sub> <sub>-</sub> = V<sub>CS</sub> <sub>+</sub> = 32V, C<sub>REF</sub> = 0.1µF, T<sub>A</sub> = +25°C, unless otherwise noted.)

V<sub>SENSE</sub> (mV)

V<sub>SENSE</sub> (mV)

### Typical Operating Characteristics (continued)

$(AV_{DD} = DV_{DD} = 5V, external\ V_{REFADC} = 2.5V, external\ V_{REFDAC} = 2.5V, V_{CS\_-} = V_{CS\_+} = 32V, C_{REF} = 0.1 \mu F, T_A = +25 ^{\circ}C, unless otherwise noted.)$

### Typical Operating Characteristics (continued)

$(AV_{DD} = DV_{DD} = 5V, external\ V_{REFADC} = 2.5V, external\ V_{REFDAC} = 2.5V, V_{CS\_-} = V_{CS\_+} = 32V, C_{REF} = 0.1\mu\text{F}, T_A = +25^{\circ}\text{C}, unless otherwise noted.})$

### Typical Operating Characteristics (continued)

$(AV_{DD} = DV_{DD} = 5V, external\ V_{REFADC} = 2.5V, external\ V_{REFDAC} = 2.5V, V_{CS\_-} = V_{CS\_+} = 32V, C_{REF} = 0.1\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

### Pin Description

| PIN                          | NAME             | FUNCTION                                                                                                                                                                                                                                                                              |  |

|------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 31                        | DGND             | Digital Ground. Connect both DGND inputs to the same potential.                                                                                                                                                                                                                       |  |

| 2                            | OPSAFE1          | Output Safe Switch Logic Input 1. Drive OPSAFE1 high to close the output safe switch and clamp GATE1 to AGND. Drive OPSAFE1 low to open the switch.                                                                                                                                   |  |

| 3                            | A0/CS            | Address-Select Input 0/Chip-Select Input. In I2C mode, this is the address-select input 0. See Table 1. In SPI mode, this is the chip-select input.                                                                                                                                   |  |

| 4                            | CNVST            | Active-Low Conversion Start Input. Drive CNVST low to begin a conversion when in clock modes 01 and 11.                                                                                                                                                                               |  |

| 5                            | SPI/I2C          | Interface-Select Input. Connect to DGND for I2C interface. Connect to DV <sub>DD</sub> for SPI interface.                                                                                                                                                                             |  |

| 6                            | ALARM            | Alarm Output                                                                                                                                                                                                                                                                          |  |

| 7                            | OPSAFE2          | Output Safe Switch Logic Input 2. Drive OPSAFE2 high to close the output safe switch and clamp GATE2 to AGND. Drive OPSAFE2 low to open the switch.                                                                                                                                   |  |

| 8                            | REFDAC           | DAC Reference Input/Output                                                                                                                                                                                                                                                            |  |

| 9                            | REFADC           | ADC Reference Input/Output                                                                                                                                                                                                                                                            |  |

| 10                           | DXP1             | Temperature Diode Positive Input 1. Connect DXP1 to the anode of the external diode.                                                                                                                                                                                                  |  |

| 11                           | DXN1             | Temperature Diode Negative Input 1. Connect DXN1 to the cathode of the external diode.                                                                                                                                                                                                |  |

| 12                           | DXP2             | Temperature Diode Positive Input 2. Connect DXP2 to the anode of the external diode.                                                                                                                                                                                                  |  |

| 13                           | DXN2             | Temperature Diode Negative Input 2. Connect DXN2 to the cathode of the external diode.                                                                                                                                                                                                |  |

| 14                           | ADCIN1           | ADC Auxiliary Input 1                                                                                                                                                                                                                                                                 |  |

| 15                           | ADCIN2           | ADC Auxiliary Input 2                                                                                                                                                                                                                                                                 |  |

| 16                           | PGAOUT2          | Programmable-Gain Amplifier Output 2                                                                                                                                                                                                                                                  |  |

| 17                           | GATE2            | Gate-Drive Amplifier Output 2                                                                                                                                                                                                                                                         |  |

| 18                           | GATE1            | Gate-Drive Amplifier Output 1                                                                                                                                                                                                                                                         |  |

| 19, 25, 30,<br>34–39, 42, 48 | N.C.             | No Connection. Not internally connected. Leave unconnected.                                                                                                                                                                                                                           |  |

| 20, 24                       | AV <sub>DD</sub> | Analog-Supply Input. Connect both AVDD inputs to the same potential.                                                                                                                                                                                                                  |  |

| 21, 22, 23                   | AGND             | Analog Ground. Connect all AGND inputs to the same potential.                                                                                                                                                                                                                         |  |

| 26                           | CS2+             | Current-Sense Positive Input 2. CS2+ is the external sense-resistor connection to the LDMOS 2 supply.                                                                                                                                                                                 |  |

| 27                           | CS2-             | Current-Sense Negative Input 2. CS2- is the external sense-resistor connection to the LDMOS 2 drain.                                                                                                                                                                                  |  |

| 28                           | CS1-             | Current-Sense Negative Input 1. CS1- is the external sense-resistor connection to the LDMOS 1 drain.                                                                                                                                                                                  |  |

| 29                           | CS1+             | Current-Sense Positive Input 1. CS1+ is the external sense-resistor connection to the LDMOS 1 supply.                                                                                                                                                                                 |  |

| 32, 33, 47                   | DV <sub>DD</sub> | Digital-Supply Input. Connect all DV <sub>DD</sub> inputs to the same potential. Connect a 0.1µF capacitor to DV <sub>DD</sub> .                                                                                                                                                      |  |

| 40                           | PGAOUT1          | Programmable-Gain Amplifier Output 1                                                                                                                                                                                                                                                  |  |

| 41                           | A2/N.C.          | Address-Select Input 2/N.C. In I <sup>2</sup> C mode, this pin is the address-select input 2. See Table 1. In SPI mode, this is a no connection pin.                                                                                                                                  |  |

| 43                           | SCL/SCLK         | Serial-Clock Input. SCL is the I2C-compatible clock input. SCLK is the SPI-compatible clock input.                                                                                                                                                                                    |  |

| 44                           | SDA/DIN          | Serial-Data Input/Output. SDA is the I2C-compatible input/output. DIN is the SPI-compatible data input.                                                                                                                                                                               |  |

| 45                           | A1/DOUT          | Address-Select Input 1/Data Out. In I <sup>2</sup> C mode, this is the address-select input 1. See Table 1. In SPI mode, this is the serial-data output. Data is clocked out on the falling edge of SCLK. DOUT is a high-impedance output when $\overline{\text{CS}}$ is driven high. |  |

| 46                           | BUSY             | Busy Output. BUSY goes high to indicate activity.                                                                                                                                                                                                                                     |  |

| _                            | EP               | Exposed Pad. Connect EP to AGND. Internally connected to AGND.                                                                                                                                                                                                                        |  |

|                              |                  |                                                                                                                                                                                                                                                                                       |  |

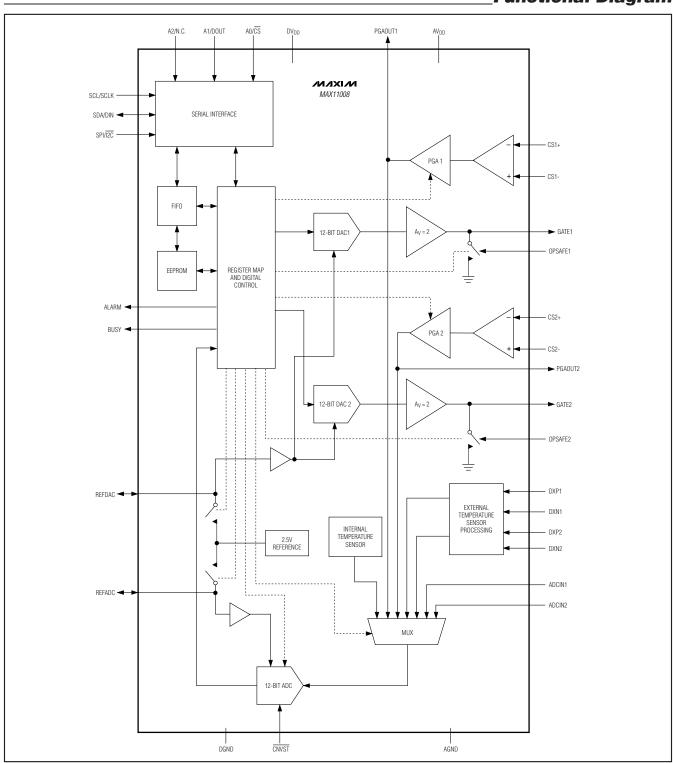

### \_Functional Diagram

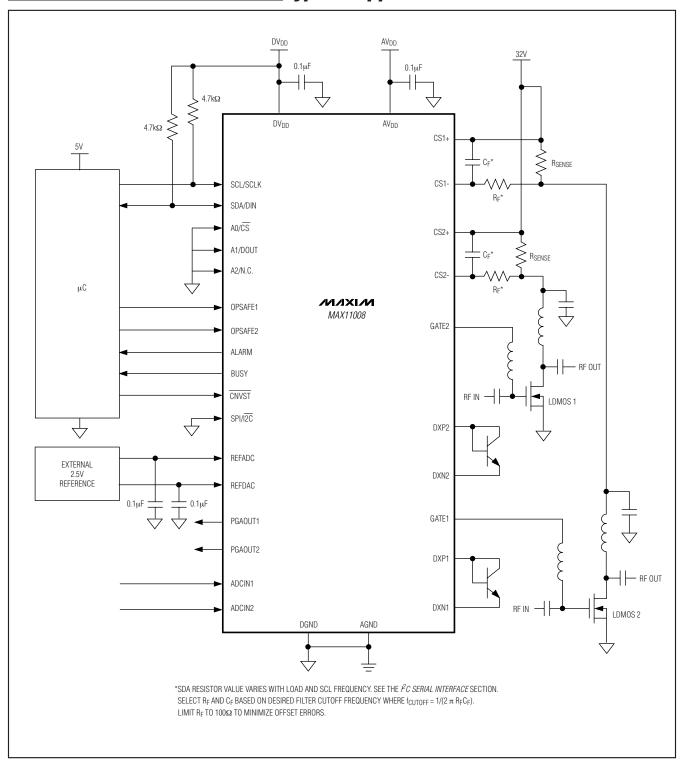

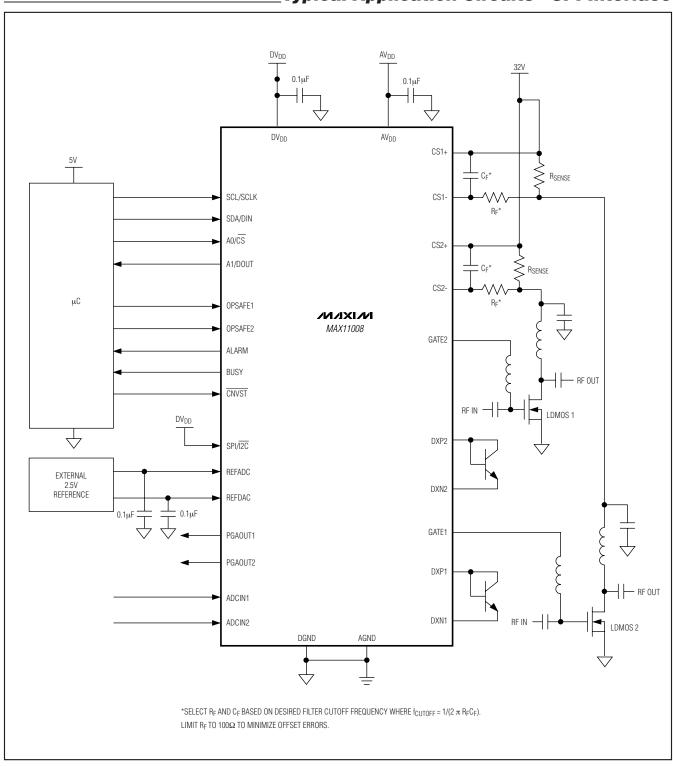

### Typical Application Circuits—I<sup>2</sup>C Interface

### Typical Application Circuits—SPI Interface

### **Detailed Description**

The MAX11008 sets and controls the bias conditions for dual RF LDMOS power devices found in cellular base-station power amps. Each device includes two high-side current-sense amplifiers with programmable gains of 2, 10, and 25 to monitor the LDMOS transistor drain current over the 20mA to 5A range. Two external diode-connected transistors monitor the LDMOS transistor temperatures while an internal temperature sensor measures the local die temperature of the MAX11008. The 12-bit ADC is interfaced to a 7:1 multiplexer and converts the signals from the PGA outputs, internal and external temperature readings, or the two auxiliary analog inputs into digital data results that can be stored in the FIFO.

On the control side, two gate-drive channels, driven from two 12-bit DACs and a gain stage of 2, generate a positive gate voltage bias for the LDMOS. Each gate-drive output supports up to  $\pm 2$ mA of gate current. The gate-drive amplifier is current-limited to  $\pm 25$ mA and features a fast clamp to analog ground that operates independently of the serial interface.

The MAX11008 includes an on-chip, nonvolatile EEPROM that stores LUTs and register information. The LUTs are designed to store gate voltage vs. temperature curves for the LDMOS FET. The data is used for temperature compensation of the LDMOS FET's bias point. The LUTs can also contain compensation data for another independent parameter: either sense voltage or AIN voltage.

### **Digital Serial Interface**

The MAX11008 features both an I<sup>2</sup>C and an SPI-compatible serial interface. Connect SPI/I2C to DGND to select the I<sup>2</sup>C serial-interface operation, or to DV<sub>DD</sub> to select the SPI serial-interface operation. Do not alter interface mode during operation.

#### SPI Serial Interface

Connect SPI/ $\overline{\rm I2C}$  to DV<sub>DD</sub> to select the SPI interface. The SPI serial interface consists of a serial data input (DIN), a serial clock line (SCLK), a chip select ( $\overline{\rm CS}$ ), and a serial data output (DOUT). The use of serial data output (DOUT) is optional and is only required when data is to be read back by the master device. The MAX11008 is SPI compatible within the range of V<sub>DD</sub> = +2.7V to +5.25V. DIN, SCLK,  $\overline{\rm CS}$ , and DOUT facilitate bidirectional communication between the MAX11008 and the master at rates up to 20MHz.

Figure 1 illustrates the 4-wire interface timing diagram. The MAX11008 is a transmit/receive slave-only device, relying upon a master to generate a clock signal. The master initiates data transfer on the bus and generates the SCLK signal to permit data transfer.

Figure 1. SPI Serial-Interface Timing

The SPI bus cycles are 24 bits long. Data can be supplied as three 8-bit bytes or as a continuous 24-bit stream.  $\overline{\text{CS}}$  must remain low throughout the 24-bit sequence. The first 8-bit byte is a command byte C[7:0]. The next 16 bits are data bits D[15:0]. Clock signal SCLK can idle low or high, but data is always clocked in on the rising edge of SCLK (CPOL = CPHA).

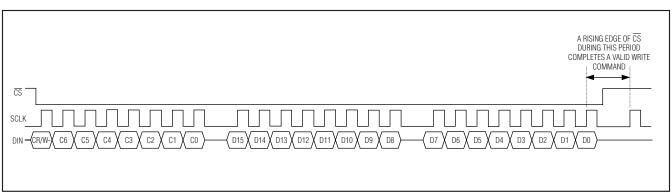

SPI data transfers begin with the falling edge of  $\overline{\text{CS}}$ . Data is clocked into the device on the rising edges of SCLK and clocked out of the device on the falling edges of SCLK. For correct bus cycles,  $\overline{\text{CS}}$  should frame the data and should not return to a 1 until after the last active rising clock edge. See Figure 2 for timing details. A rising edge of  $\overline{\text{CS}}$  causes DOUT to three-state and data reads should be performed accordingly. See Figures 1 and 3.

When writing instructions to the MAX11008, 24 clock cycles must be completed before  $\overline{\text{CS}}$  is driven high. The MAX11008 executes the instruction only after the 24th clock cycle has been received and  $\overline{\text{CS}}$  is driven high. To abort unwanted instructions,  $\overline{\text{CS}}$  can be driven high at any time before the 23rd rising clock edge.

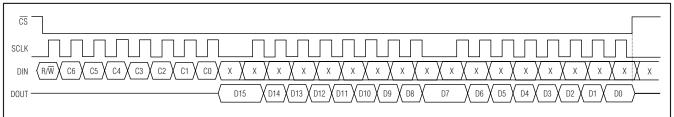

When reading data from the MAX11008, 24 clock cycles must be completed before  $\overline{CS}$  is driven high. If  $\overline{CS}$  is driven high before the completion of the 24th falling edge, DOUT immediately three-states, the interface resets in preparation for the next command, and the data being read is lost.

#### Write Format

Use the following sequence to write 16 bits of data to a MAX11008 register (see Figure 2):

- 1) Drive  $\overline{CS}$  low to select the device.

- 2) Send the appropriate write command byte (see Table 6 for the register address map). The command byte is clocked in on the rising edge of SCLK.

- 3) Send 16 bits of data D[15:0] starting with the most significant bit (MSB). Data is clocked in on the rising edges of SCLK.

- 4) Drive  $\overline{\text{CS}}$  high to conclude the command.

Figure 2. SPI Write Sequence

#### Read Format

Use the following sequence to read 16 bits of data from a MAX11008 register (see Figure 3):

- 1) Drive  $\overline{CS}$  low to select the device.

- Send the appropriate read command byte (see Table 6 for the register address map). The command byte is clocked in on the rising edges of SCLK.

- Receive 16 bits of data. The first 4 bits of data are always high. Data is clocked out on the falling edges of SCLK.

- 4) Drive CS high.

#### I<sup>2</sup>C Serial Interface

Connect SPI/ $\overline{I2C}$  to DGND to select the I<sup>2</sup>C interface. The I<sup>2</sup>C serial interface consists of a serial data line (SDA) and a serial clock line (SCL). The MAX11008 is I<sup>2</sup>C compatible within the DV<sub>DD</sub> = 2.7V to 5.25V range. SDA and SCL facilitate bidirectional communication between the MAX11008 and the master at rates up to 400kHz for fast mode and up to 3.4MHz for high-speed mode (HS mode). See the *Bus Timing* and *HS I<sup>2</sup>C Mode* sections for more information on data-rate configurations.

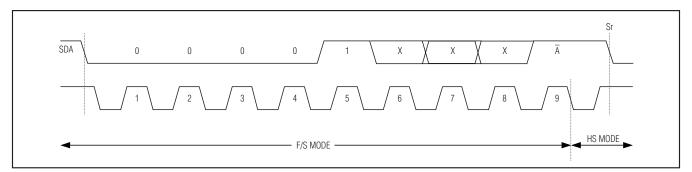

Figure 4 shows the 2-wire interface timing diagram. The MAX11008 is a transmit/receive slave-only device, relying upon a master to generate a clock signal. The master (typically a microcontroller) initiates data transfers on the bus and generates the SCL signal to permit data transfer.

Figure 3. SPI Read Sequence

Figure 4. I<sup>2</sup>C Serial-Interface Timing Diagram

A master device communicates to the MAX11008 by transmitting the proper slave address followed by a command and/or data words. Each transmit sequence is framed by a START (S) or repeated START (Sr) condition and a STOP (P) condition. Each word transmitted over the bus is 8 bits long and is always followed by an acknowledge clock pulse.

The MAX11008 SDA and SCL drivers are open-drain outputs, requiring a pullup resistor ( $750\Omega$  or greater) to generate a logic-high voltage (see the *Typical Application Circuits*). Series resistors are optional for noise filtering. These series resistors protect the input stages of the MAX11008 from high-voltage spikes on the bus line, and minimize crosstalk and undershoot of the bus signals.

#### Bit Transfer

One data bit is transferred during each SCL clock cycle. The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high are control signals (see the *START and STOP Conditions* section). Both SDA and SCL idle high when the I<sup>2</sup>C bus is not busy.

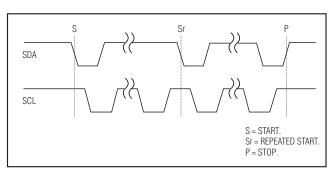

#### START and STOP Conditions

The master initiates a transmission with a START condition (S), which is a high-to-low transition on SDA while

Figure 5. START and STOP Conditions

SCL is high. The master terminates a transmission with a STOP condition (P), which is a low-to-high transition on SDA while SCL is high (see Figure 5). A repeated START condition (Sr) can be used in place of a STOP condition to leave the bus active and the mode unchanged (see the *HS I2C Mode* section).

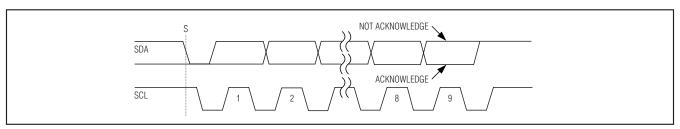

# Acknowledge Bits and Not-Acknowledge Conditions Data transfers are framed with an acknowledge bit (ACK) or a not-acknowledge bit (NACK). Both the master and the MAX11008 (slave) generate acknowledge bits. To generate an acknowledge, the receiving device must pull SDA low before the rising edge of the acknowledge-related clock pulse (ninth clock pulse) and keep it low during the high period of the clock pulse (see Figure 6).

To generate a not-acknowledge condition, the receiver allows SDA to be pulled high before the rising edge of the acknowledge-related clock pulse, and leaves SDA high during the high period of the clock pulse. Monitoring the acknowledge bits allows for detection of unsuccessful data transfers. An unsuccessful data transfer happens if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master reattempts communication at a later time.

Figure 6. Acknowledge Bits

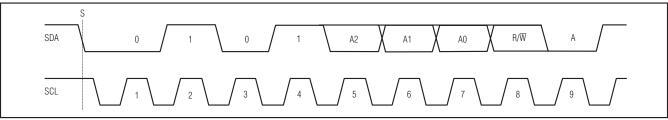

#### Slave Address

A bus master initiates communication with a slave device by issuing a START condition followed by the 7-bit slave address and a read/write (R/W) bit (see Figure 7). When the device recognizes its slave address, it is ready to accept or send data depending on the R/W bit. When the MAX11008 recognizes its slave address, it issues an ACK by pulling SDA low for one clock cycle and is ready to accept or send data depending on the R/W bit that was sent.

The MAX11008 has eight user-selectable slave addresses, which are set through inputs A0, A1, and A2 (see Table 1). This feature allows up to eight MAX11008 devices to share the same bus inputs. The 4 MSBs D[7:4] are factory set, and the 3 LSBs are user-selectable.

#### **Table 1. Slave Address Select**

| A2 | <b>A</b> 1 | A0 | ADDRESS |

|----|------------|----|---------|

| 0  | 0          | 0  | 0101000 |

| 0  | 0          | 1  | 0101001 |

| 0  | 1          | 0  | 0101010 |

| 0  | 1          | 1  | 0101011 |

| 1  | 0          | 0  | 0101100 |

| 1  | 0          | 1  | 0101101 |

| 1  | 1          | 0  | 0101110 |

| 1  | 1          | 1  | 0101111 |

#### Bus Timing

At power-up, the bus timing is set for I<sup>2</sup>C fast-mode (F/S mode), which allows I<sup>2</sup>C clock rates up to 400kHz. The MAX11008 can also operate in high-speed mode (HS mode) to achieve I<sup>2</sup>C clock rates up to 3.4MHz. See Figure 4 for I<sup>2</sup>C bus timing.

#### HS I<sup>2</sup>C Mode

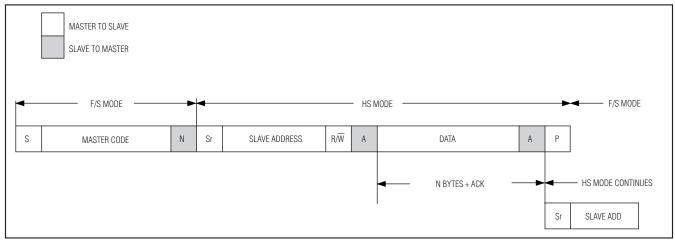

Select HS mode by addressing all devices on the bus with the HS-mode master code 0000 1XXX (X = don't care). After successfully receiving the HS-mode master code, the MAX11008 issues a NACK, allowing SDA to be pulled high for one clock cycle (see Figure 8). After the NACK, the MAX11008 operates in HS mode. The master must then send a repeated START (Sr) followed by a slave address to initiate HS-mode communication. If the master generates a STOP condition, the

Figure 7. Slave Address Bits

Figure 8. F/S-Mode to HS-Mode Transfer

MAX11008 returns to F/S mode. Use a repeated START condition in place of a STOP condition to leave the bus active and the mode unchanged. Figure 9 summarizes the data bit transfer format for HS-mode communication.

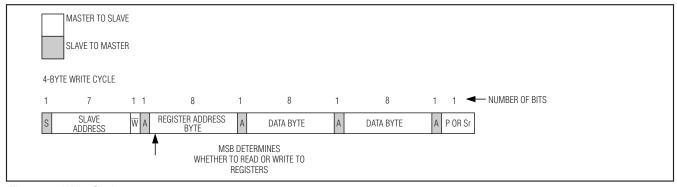

#### Register Address/Data Bytes (Write Cycle)

A write cycle begins with the bus master issuing a START condition followed by 7 address bits (see Figure 5 and Table 1) and a write bit  $(R/\overline{W}=0)$ . Once the slave address is recognized and the write bit is received, the MAX11008 (I<sup>2</sup>C slave) issues an ACK by pulling SDA low for one clock cycle. The master then sends the register address byte (command byte) to the

slave. The MSB of the register address byte is the read/write bit for the destination register address of the slave and must be set to 0 for a write cycle (see the *Register Address Map* section). After receiving the byte, the slave issues another acknowledge, pulling SDA low for one clock cycle. The master then writes two data bytes, receiving an ACK from the slave after each byte is sent. The master ends the write cycle by issuing a STOP condition. When operating in HS mode, a STOP condition returns the bus into F/S mode (see the *HS I2C Mode* section). Figure 10 shows a complete write cycle.

Figure 9. Data-Transfer Format in HS Mode

Figure 10. Write Cycle

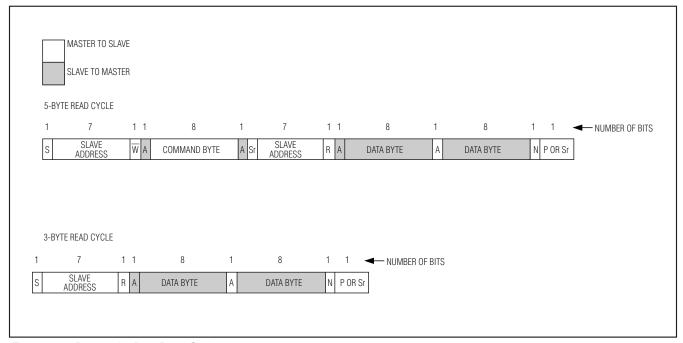

#### Register Address/Data Bytes (5-Byte Read Cycle)

A read cycle begins with the master issuing a START condition followed by a 7-bit address, (see Figure 5 and Table 1) and a write bit  $(R/\overline{W} = 0)$  to instruct the MAX11008 interface that it is about to receive data. Once the slave address is recognized and the write bit is received, the MAX11008 (I2C slave) issues an ACK by pulling SDA low for one clock cycle. The master then sends the register address byte (command byte) to the slave. The MSB of the register address byte is the read/write bit for the destination register address of the slave and must be set to 1 for a read cycle (see the Register Address Map section). After this byte is received, another acknowledge bit is sent to the master from the slave. The master then issues a repeated START (Sr) condition. Following a repeated START (Sr), the master writes the slave address byte again with a read bit  $(R/\overline{W} = 1)$ . After a third acknowledge signal from the slave, the data direction on the SDA bus reverses and the slave writes the 2 data bytes (the contents of the register that was addressed in the previous command byte) to the master. Finally, the master issues a NACK followed by a STOP condition (P), ending the read cycle. Figure 11 shows a complete 5-byte read cycle.

### Default Read Cycle (3-Byte Read Cycle)

The MAX11008 2-wire interface has a unique feature for read commands. To avoid the necessity of sending 2 slave address bytes in one read cycle (see the 5-byte read cycle in Figure 11), the MAX11008 2-wire interface recognizes a single slave address byte with a read bit  $(R/\overline{W}=1)$ . In this case, the interface outputs the contents of the last read device register. This default read feature is useful when the master must perform multiple consecutive reads from the same device register. Figure 11 shows a complete 3-byte read cycle.

Figure 11. 5-Byte and 3-Byte Read Cycle

#### 12-Bit ADC

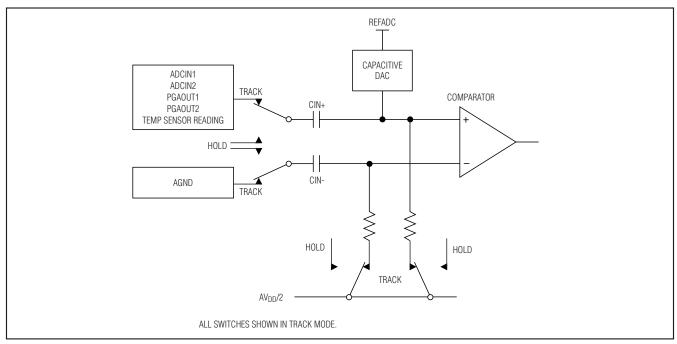

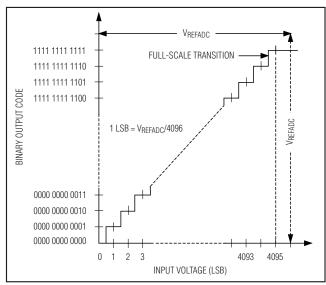

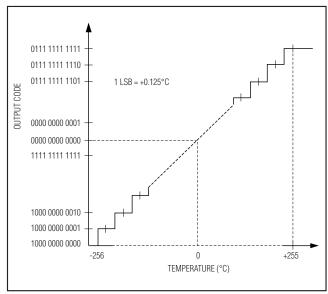

The MAX11008 12-bit ADC uses a SAR conversion technique and on-chip track-and-hold (T/H) circuitry to convert the PGA outputs (PGAOUT1 and PGAOUT2), temperature measurements, and single-ended auxiliary input voltages (ADCIN1 and ADCIN2) into 12-bit digital data when in ADC monitor mode (see the *Hardware Configuration Register (HCFIG) (Read/Write)* section). All nontemperature measurements are converted using a unipolar transfer function (see Figure 13), and all temperature measurements are converted using a bipolar transfer function (see Figure 14).

#### Analog Input T/H

Figure 12 shows the equivalent circuit for the ADC input architecture of the MAX11008. In track mode, an input capacitor is connected to the input signal (ADCIN1, ADCIN2, PGAOUT1, PGAOUT2, or temperature sensor processor output). Another input capacitor is connected to AGND. After the T/H enters hold mode, the difference between the sampled positive and negative input voltages is converted. The charging rate of the input capacitance determines the time required for the T/H to acquire an input signal. If the input signal's source impedance is high, the required acquisition time lengthens accordingly.

Any source impedance below  $300\Omega$  does not affect the ADC's AC performance. A high-impedance source can be accommodated either by lengthening taco or by placing a 1µF capacitor between the positive and negative analog inputs. The combination of the analoginput source impedance and the capacitance at the analog input creates an RC filter that limits the analog input bandwidth.

#### Input Bandwidth

The ADC's input-tracking circuitry has a 1MHz small-signal bandwidth, to digitize high-speed transient events and measure periodic signals with bandwidths exceeding the ADC's sampling rate by using undersampling techniques. Anti-alias filtering of the input signals is necessary to prevent high-frequency components from aliasing into the frequency band of interest.

#### Analog Input Protection

Internal electrostatic-discharge (ESD) protection diodes clamp all analog inputs to AVDD and AGND, allowing the inputs to swing from (AGND - 0.3V) to (AVDD + 0.3V) without damage. However, for accurate conversions near full scale, the inputs must not exceed AVDD by more than 50mV or be lower than AGND by 50mV. If an analog input voltage exceeds the supplies, limit the input current to 2mA.

Figure 12. Analog Input Track and Hold

#### **ADC Transfer Functions**

Figure 13 shows the unipolar transfer function for non-temperature measurements, and Figure 14 shows the bipolar transfer function used for temperature measurements. Code transitions occur halfway between successive-integer LSB values. Output coding is binary, with 1 LSB = VREFADC/4096 for nontemperature measurements, and 1 LSB = +0.125°C for temperature measurements. All signed binary results use two's complement format.

Figure 13. ADC Transfer Function

Figure 14. Temperature Transfer Function

#### ADC Conversion Scheduling

The MAX11008 ADC multiplexer scans and converts the selected inputs in the order shown in Table 2 (see the *ADC Conversion Register (ADCCON) (Write Only)* section) when more than one channel is selected. The results are stored in the FIFO when in ADC monitoring mode. The BUSY signal is set at the start and reset at the end of a scan except when the continuous convert bit is set at which time BUSY does not then respond to ADC conversions.

Writing a conversion command before a conversion is complete cancels the pending conversion. Avoid addressing the device using the serial interface while the ADC is converting.

### **Table 2. Order of ADC Conversion Scan**

| ORDER OF SCAN | DESCRIPTION OF CONVERSION         |

|---------------|-----------------------------------|

| 1             | Internal device temperature       |

| 2             | External diode 1 temperature      |

| 3             | Output of PGA 1 for current sense |

| 4             | Auxiliary input 1 (ADCIN1)        |

| 5             | External diode 2 temperature      |

| 6             | Output of PGA 2 for current sense |

| 7             | Auxiliary input 2 (ADCIN2)        |

#### **ADC Clock Modes**

The MAX11008 offers three conversion/acquisition modes (known as clock modes) selectable through configuration register bits CKSEL1 and CKSEL0.

If the ADC conversion requires the internal reference (temperature measurement or voltage measurement with internal reference selected) and the reference has not been previously forced on (FBGON = 1), the device inserts a typical delay of 72µs, for the reference to settle, before commencing the ADC conversion. The reference remains powered up while there are pending conversions. If the reference is not forced on, it automatically powers down at the end of a scan or when CONCONV in the ADC Conversion register is set back to 0.

### Internally Timed Acquisitions and Conversions

### Clock Mode 00

In clock mode 00, power-up, acquisition, conversion, and power-down are all initiated by writing to the ADC Conversion register and performed automatically using the internal oscillator. This is the default clock mode. The ADC sets the BUSY output high, powers up, and scans all requested channels storing the results in the FIFO if the ADCMON bit has been set. After the scan is

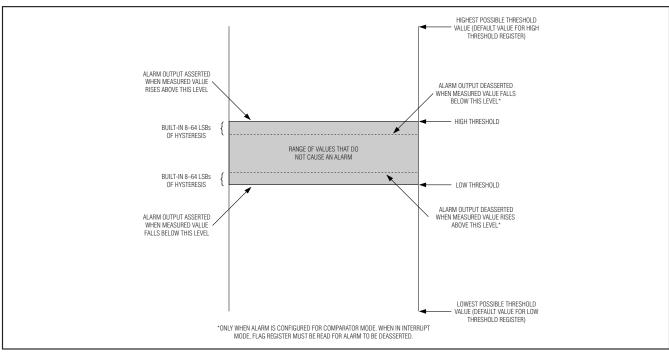

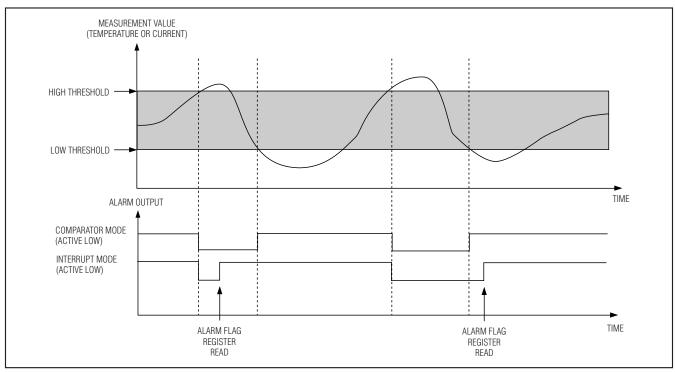

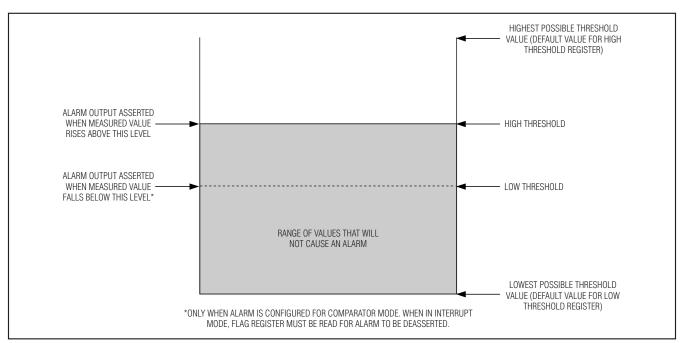

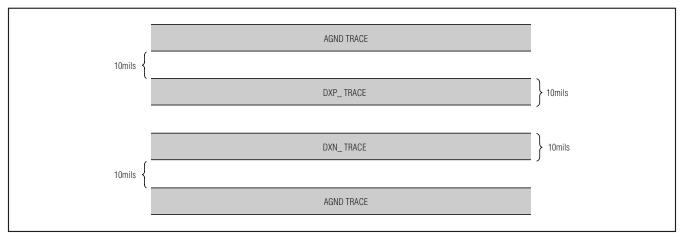

complete the ADC powers down, BUSY is pulled low, and the results for all of the selected channels are available in the FIFO.